# Hierarchical Fault Tracing VLSI Sequential Circuit by Successive Circuit Extraction from CAD Layout Data

K. Miura<sup>(a)</sup> K. Nakamae<sup>(a)</sup> H. Fujioka<sup>(b)</sup>

<sup>a)</sup>Dept. Information Systems Engineering, Grad. Sch. Information Science and Technology, Osaka University

b) Dept. Management and Information Science, Fukui University of Technology

Abstract: A hierarchical VLSI fault tracing method is proposed which is applicable to the case where only CAD layout data is available in the CAD-linked electron beam test system. The CAD layout data is assumed to be hierarchically structured. The method uses the expansion of a previously proposed integrated algorithm which combines a transistor-level fault tracing algorithm and a successive circuit extraction from a non-hierarchically or a flat structured CAD layout data. The method allows us to trace a fault hierarchically from the top level cell to the lowest primitive cell and from the primitive cell to the transistor-level circuit in a consistent manner independent of circuit functions even when the cell data and the transistor-level circuit data exist in a level as a mixture. An application of the method to a hierarchically structured CMOS model layout with about 600 transistors shows its validity.

Keywords: fault tracing, CAD layout data, successive circuit extraction, sequential circuit, benchmark circuit

# 1. Introduction

Please write an introduction of your research here. Please cite reference articles as this [1]-[3]. Please write an introduction of your research here. Please write an introduction of your research here.

# 2. First Level Section Title

# 2.1 Second Level Section Title

### 2.1.1 Third Level Section Title

Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your re-

search here. Please explain on your research here.

Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your research here.

#### 2.1.2 Third Level Section Title

Please explain on your research here. Please explain on your research here.

#### 2.2 Second Level Section Title

Please explain on your research here. Please explain on your research here. Please explain on your research here. Please explain on your re-

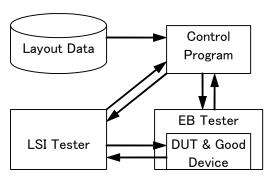

Fig. 1 An example of the figure

search here. Please explain on your research here.

## 3. First Level Section Title

Please explain on your research here. Please explain on your research here.

# 4. Conclusions

Please conclude your research here. Please conclude your research here.

Table 1 An example of the table

| Circuit | # of transis- | # of probing |

|---------|---------------|--------------|

| name    | tors          | points       |

| S27     | 136           | 6.6          |

| S208    | 676           | 14.9         |

| S298    | 1006          | 10.9         |

# Acknowledgements

Please write acknowledgements if needed. Please write acknowledgements if needed. Please write acknowledgements if needed. Please write acknowledgements if needed.

# References

- [1] K. Miura, K. Nakamae and H. Fujioka, "Automatic transistor-level performance fault tracing by successive circuit extraction from CAD layout data for VLSI in the CAD-linked EB test system," *IEICE Trans. Electron.*, vol.E78-C, no.11, pp.1607-1617, Nov. 1995.

- [2] Y. Midoh, K. Miura, K. Nakamae, and H. Fujioka, "Statistical Optimization of the Canny Edge Detector for Measurement of Fine Line Patterns in the SEM Image of LSI," *Meas. Sci. Technol.*, 16, 2, pp. 477–487 Feb. 2005.

- [3] K. Miura, M. Fujita, K. Nakamae and H. Fujioka, "Pattern Matching Between an SEM Exposed Pattern Image of LSI Fine Structures and CAD Layout Data by Using the Relaxation Method," in Proc. 49th International Conference on Electron, Ion, and Photon Beam Technology and Nanofabrication (EIPBN), Orland, USA, pp. 166-167, May 2005.

# Apepndix A

Please write appendant descriptions here if needed. Please write appendant descriptions here if needed.